TAA320

|

|

|||||||||||||||||||||||||||||||||||

|

Hits: 1550 Replies: 0

VALVO TAA320 - das glücklose IC mit MOS-FET Eingang

|

|

|

Harald Giese

04.Feb.22 |

1

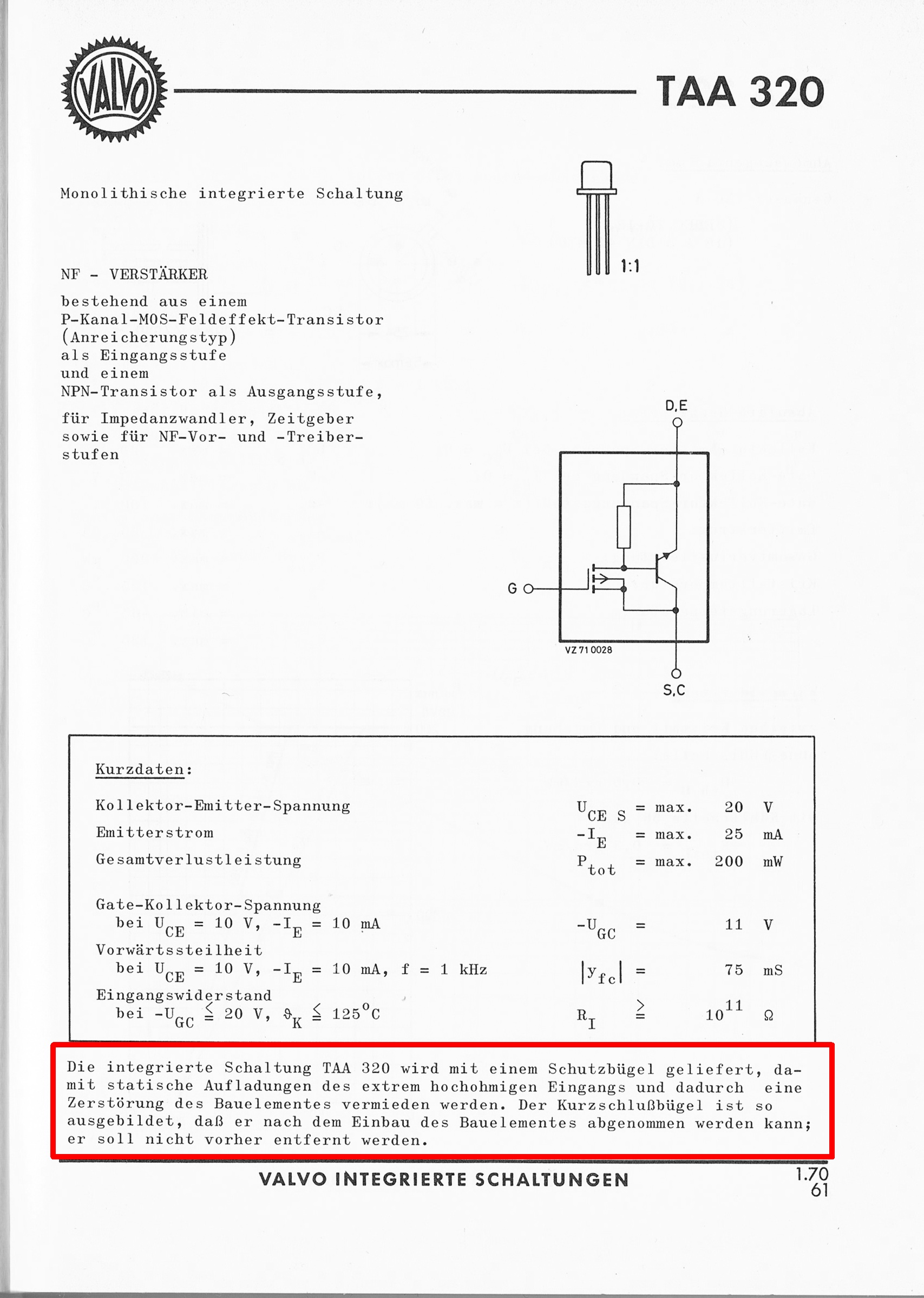

VALVO TAA320 - das glücklose IC mit MOS-FET EingangAlle Bilder können duch Anklicken vergrößert werden 1 VorgeschichteIn den von VALVO herausgegebenen "Technischen Informationen für die Industrie" (im folgenden kurz "TI" genannt) konnte man in der Nr. 115 vom März 1968 mit dem Titel "Lineare Integrierte Schaltungen" folgende vielversprechende Produktankündigung für den TAA320 lesen:

Natürlich dachte man bei so hohem Eingangswiderstand intuitiv an eine Anwendung in Elektrometer - Verstärkern für die Messung geringster Ladungsmengen im nC (Nano-Coulomb) Bereich, in "Sample-and-Hold" - Schaltungen, wo es auf die lange Zwischenspeicherung eines Spannungsniveaus ankommt, oder ganz profan an Vorverstärker für Kristalltonabnehmer. Legt man einen Kondensator von 1 µF an das Gate des TAA320, so entlädt sich dieser mit einer Zeitkonstante τ = RC= 108 s ≈ 3 Jahre. Man hat also einen nahezu "nicht flüchtigen" Speicher. Der Leckstrom des Kondensators ist wahrscheinlich größer als der durch die Gate-Elektrode. Anhänger der Röhrentechnik witterten eine Renaissance der guten alten Vakuumröhre mit ihrer leistungslosen Steuerung, aber jetzt noch kleiner als ein Nuvistor und ohne Nowendigkeit einer Heizung. Um diese neuartige Integriere Schaltung für einen möglichst weiten potentiellen Kundenkreis attraktiv zu machen, erschien schon im Folgemonat April 1968 die TI 117 , 10 Monate später, im Februar 1969 die TI 123:

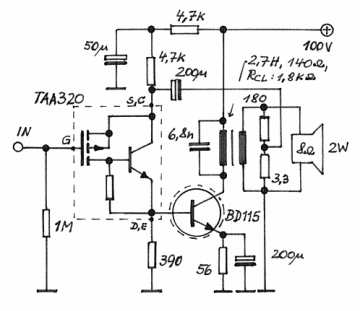

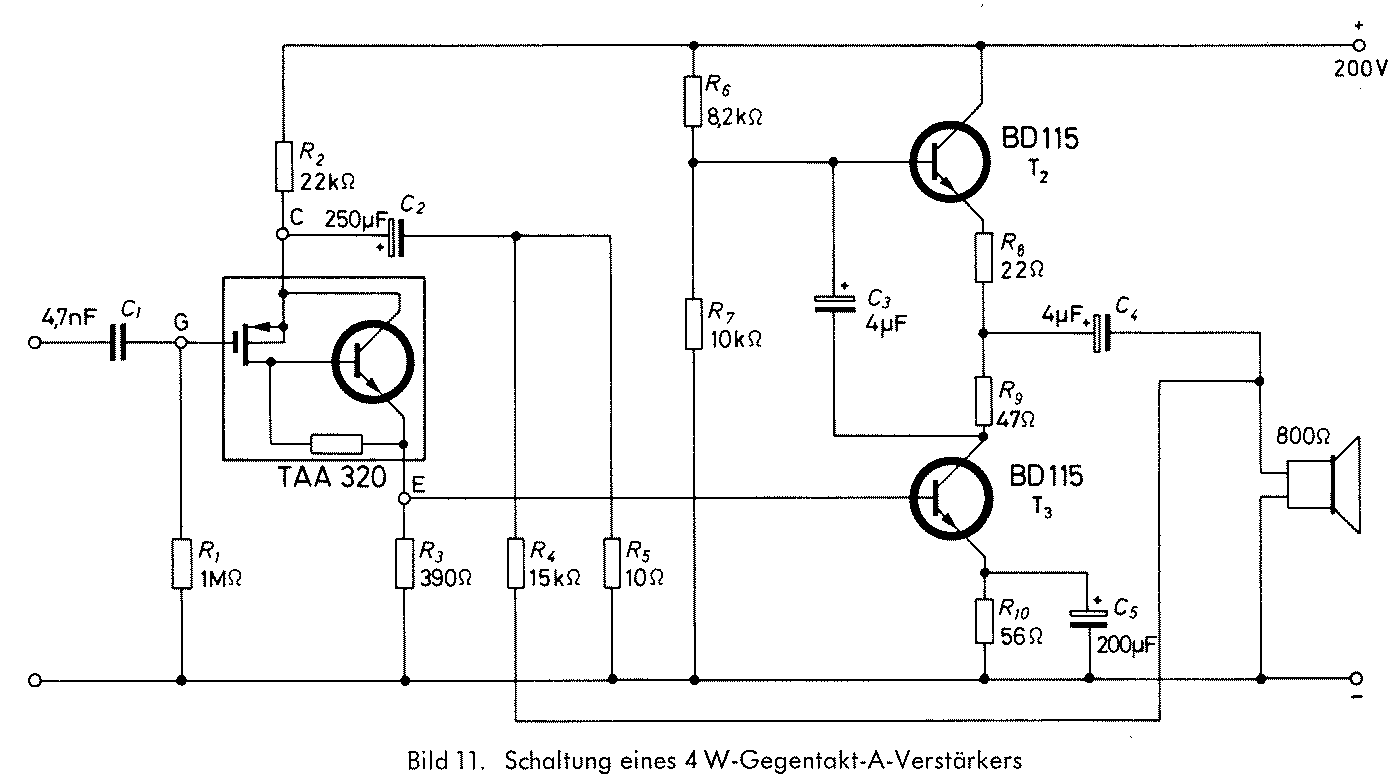

Einige der in diesen Broschüren gezeigten Schaltungen greife ich hier heraus Bilder aus TI117 Bilder aus TI123 Langzeitschalter NF - Verstärker

Wie schon gesagt, handelte es sich hier um Technische Informationen für die Industrie, also um eine Vorabinformation über Produkte die man demnächst erwarten konnte. Die später in den VALVO Handbüchern veröffentlichten Daten des TAA320 wichen dann etwas davon ab. Z.B. waren für den Eingangswiderstand und die Steilheit nun etwas niedrigere Werte angegeben: Steilheit = 75mA / V und DC - Eingangswiderstand RI ≥ 1011 Ω .

Ein Detail auf der Seite 61 des Handbuchs von 1971, das zunächst nicht besonders ins Auge sprang, habe ich rot hervorgehoben. Dort kann man lesen, dass die 3 Anschlüsse des TAA320 mit einem Kurzschlussbügel versehen wurden (später mit einem graphitierten Gummiband umspannt), um für ständigen Potentialausgleich zwischen den 3 Anschlüssen zu sorgen und somit eine elektrostatische Aufladung des Gate - Anschlusses gegenüber den anderen Anschlüssen auszuschließen. Erst nach Einbau und Verbindung mit den anderen Schaltungselementen durfte der Kurzschluss entfernt werden.Das fanden die Kunden nicht besonders originell, denn dieses subtile Detail war in den TI nicht erwähnt worden. So entpuppte sich dieser unscheinbare Zusatz letzten Endes als "Show - Stopper" für den Vertrieb dieses ICs.

Schaut man heute im RM nach Modellen, in denen der TAA320 eingsetzt wurde, findet man nur:

Natürlich könnten noch weitere Modelle existieren, die den TAA320 verwendeten. Im RM sind z.Zt. jedoch keine weiteren aufgeführt. Laut Auskunft des ehemaligen Entwicklers Hans M. Knoll, hat GRUNDIG, obwohl damals enger Geschäftspartner und einer der größten Abnehmer von VALVO Produkten, den TAA320 nie eingesetzt. Auf jeden Fall brachte das Hantieren mit diesen MOS Bausteinen Probleme mit sich, die offensichtlich viele Firmen davon abgehalten haben, den TAA320 einzusetzen. Das möchte ich anhand unserer Prüfarbeiten im VALVO - Qualitätslabor schildern

2 Die Aufgaben des QualitätslaborsMein erster Arbeitsplatz nach dem Physikstudium an der TU Berlin war in den Jahren 1970 - 1972 im RHW (Röhren- und Halbleiterwerk) der VALVO in Hamburg-Lokstedt. Da im PHILIPS - Applikationlabor gerade keine freie Stelle verfügbar war, hatte man mich im Qualitätslabor der Halbleiterfertigung untergebracht - und zwar im Bereich "Integrierte Techniken - MOS Technologie" (QL-IT_MOS). Das Qualitätslabor ist - wie der Name schon erahnen lässt, verantwortlich für die Einhaltung der in den Datenbüchern propagierten mechanischen und elektrischen Daten eines Produkts. Dazu zieht man aus der laufenden Produktion Probechargen und misst die in den Datenbüchern angegebenen Werte nach. Natürlich nicht alle bei jeder Probecharge! Schon bei Transistoren war die Prüfprozedur recht aufwendig. Abhängig vom Typ umfassten die Prüfpunkte nicht nur die Gleichstrom- und HF - Parameter wie z.B. Betriebsströme unter Standard - Betriebsbedingungen, Leckströme und Transistfrequenz, sondern auch die Verzinnbarkeit der Anschlussdrähte und die Parameterkonstanz nach Hochtemperaturlagerung. Man musste ja sicherstellen, dass die Transistoren nach langer Lagerzeit und dem Schwallbad - Lötprozess nicht lose in den Platine steckten. Um die elektrische Prüfprozedur etwas zu vereinfachen, hatte man für die Routineprüfung der Integrierten Schaltungen eine vereinfachte Strategie entwickelt, die sich als äußerst erfolgreich erwies. Man hatte über größere Stückzahlen hinweg die in die verschiedenen Pins fließenden DC - Ströme gemessen und festgestellt, dass diese ein hervorragender Indikator für die Einhaltung der Betriebsparameter waren. Nur noch bei viel kleineren Chargen wurden auch die in den Handbüchern publizierten DC - und AC - Betriebsparameter gemessen. Die zuvor genannten einfachen DC - Messungen wurden weitgehend automatisiert. Das IC wurde in eine hochqualitative Fassung mit vergoldeten Federbronze - Kontakten und Klemm- Mechanik gesteckt und eine Ablaufsteuerung legte die erforderlichen Spannungen über REED - Kontate an die betreffenden Pins. DC - Stromanzeigen zeigten den Labor - Assistenten sehr schnell, ob eine Anomalie vorlag und man eine Fertigungsscharge eventuell zurückhalten sollte. Links sieht man eine solche Schnellprüffassung. Der auf beiden Seiten aus der Fassung herausragende 2 mm - Vierkantstift wurde mit einem entsprechenden Schlüssel um 90° gedreht, woraufhin sich der äußere Rahmen durch einen Exzentermechanismus auf- und abbewegte und damit die Klemmfedern öffnete (oben) oder zusammendrückte (unten).

Alles funktionierte problemlos bis die ersten MOS - ICs wie z.B. der TAA320 im QL-IT-MOS auftauchten. Hierfür war der übliche Messautomat nämlich nicht mehr verwendbar. Häufig genügte schon eine bloße Berührung der Anschlussdrähte mit den Fingern, um die empfindliche Gate - Kapazität infolge elektrostatischer Aufladung durchschlagen zu lassen. Die Laborassisten waren auf solche Arbeiten nicht vorbereitet, und viele MOS - ICs wurden anfangs durch unsachgemäßes Hantieren zerstört. Als einzigen Ausweg aus deser Misere sahen wir das "Anketten" der Kollegen. Die Arbeitsflächen wurden mit Metallplatten belegt, und diese mit dem Netz-Schutzleiter und den Gehäusen aller Messgeräte verbunden. Die Prüfer waren verpflichtet, ein metallisches Armband zu tragen, das über eine flexible Litze mit der metallischen - Arbeitsplatte verbunden war. Trotzdem genügte manchmal die durch bloßes Herumrutschen auf dem Bürostuhl oder die durch das Tragen von NYLTEST Hemden oder anderen Kunstfaser - Kleidungsstücke erzeugte statische Elektrizität, um MOS - Bausteine zu zerstören. Abhängig von der Oberflächenleitfähikeit der Haut oder auch der Luftfeuchte gelangte trotz Ankettens eine ausreichende Elektrizitätsmenge auf den Gateanschluss und zerstörte die Isolierschicht. Dabei muss man sich klarmachen, dass bei einer spezifizierten Gate-Kapazität von 8 pF bereits eine winzige Ladungsmenge von nur 160 pC (160 Pico Coulomb entsprechen einem Stromfluss von 1 µA für 160 µs) ausreichte, um die max. zulässige Gate - Spannung von 20 V zu überschreiten.

3 SchlussbemerkungenIch habe versucht darzustellen, wie diffizil die Handhabung früher MOS Feldeffekt Baulemente war. Selbst in Labors mit ausgeklügelten Schutzmaßnahmen kam es häufig zu Ausfällen. Ein zusätzliches Problem bei der Vermarktung solcher Bauelemente Anfang der 1970er Jahre stellte die Tatsache dar, dass bereits die ersten Sperrschicht - Feldeffekt Transistoren auf dem Markt erschienen, bei denen es diese auf elektrostatischer Aufladung basierenden Probleme nicht gab. Im Gegensatz zum MOS - FET (Metall -Oxid -Semiconductor) wird beim Sperrschicht (Junction) - FET die Stromsteuerung im Source - Drain - Kanal durch die von einem gesperrten PN - Übergang erzeugte Raumladung bewirkt. Aufgrund des durch den PN Übergang fließenden Sperrstroms haben diese Transistoren zwar einen viel niedrigeren Eingangswiderstand als MOS - FETs, aber die Verbraucher sahen dies offenbar in den meisten Anwendungen als das kleinere Übel an. Natürlich gab es auch weiterhin MOS - FETs auf dem Markt. Inzwischen hatte man aber verstanden, dass man dem Anwender unmöglich das diffizile Handling zumuten konnte - man hatte ja die schmerzhafte Erfahrung gemacht, dass sich so sensible Produkte wie der TAA320 kaum vermarkten lassen. So gab es bald MOS-FETs mit integrierten gegensinnig gepolten Gate - Schutzdioden wie z.B. den damals sehr erfolgreihen RCA Dual - Gate MOS-FET 40673. Benötigte man ein Bauelement mit höherer Steilheit, konnte man diese geschützen MOS - FETs nach Belieben extern mit bipolaren Trasistoren kaskadieren - so wie es im TAA320 intern gelöst wurde. Anmerken muss man hier noch, dass die Schutzwirkung dieser bald standardmäßig eingesetzten Gate - Dioden natürlich auch Grenzen kannte. Trafen zu große Spannungen / Ladungsmengen auf das Gate, so wurden die Schutzdioden zerstört. Als letzten Punkt möchte ich erwähnen, dass es auch Hochleistungs - MOS - FETs gibt, die ohne Schutzdioden auskommen. Das liegt daran, dass diese Bauelemente sehr große räumliche Strukturen aufweisen. Die Gate - Kapazität liegt dadurch im Bereich vieler Nanofarad, also um einen Faktor 1000 ... 10 000 höher als z.B. beim TAA320. Dadurch verursachen auch größere auf das Gate treffende Ladungsmengen nur einen moderaten Anstieg der Gatespannung (ΔU = ΔQ /C) und das Durchschlagsrisiko ist entsprechend geringer. Wie lange der "glücklose" TAA320 noch im Vertriebsprogramm der VALVO auftauchte kann ich nicht sagen, da mir die späteren Handbücher fehlen. Auf jeden Fall hatte man hier wertvolle Erfahrungen im Bereich der MOS - FET Technologie gesammelt, von der die weiteren Entwicklungen profitierten. Harald Giese |

End of forum contributions about this tube

| Data Compliance | More Information |